Böyle efsanevi bir devre için yeni bir açıklama bulmak büyük bir zorluk çünkü herkes op-amp entegratörünün ne olduğunu biliyor. Ancak belirli bir devre çözümünü bilmek, onu gerçekten anladığınız anlamına gelmez. Bir devreyi (derinlemesine) anlamak daha fazlası anlamına gelir - arkasındaki birçok özel devre uygulamasını (op-amp, BJT, FET, tube ...) birbirine bağlayan genel fikri görmek elektrik uygulamaları ...

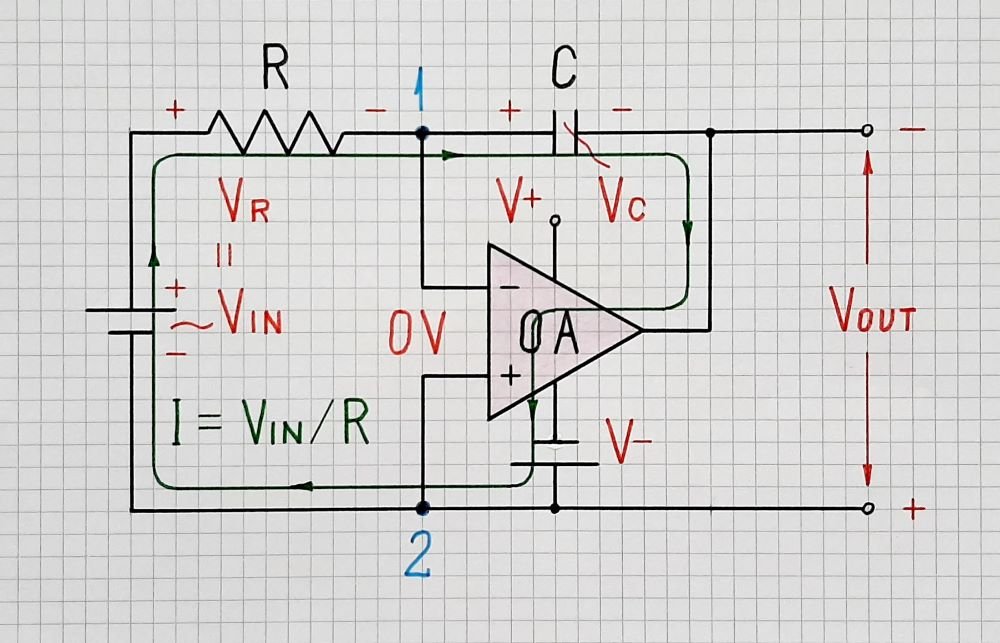

1. Op-amp ters çeviren entegratör. Bu devre çözümünün arkasındaki fikir son derece basit ve sezgiseldir. Paradoksal gelebilir ... ama onu görmek için sadece toprak sembolünü devre şemasından kaldırmanız gerekir. Şekil 1'de görebileceğiniz gibi, sadece sanal zeminin (1) ve gerçek zeminin (2) yerini etiketledim ... ve Artık bu isimleri kullanmıyorum. Sanal zemin olmadığını anlıyorsunuz çünkü gerçek bir zemin yok. Ancak yine de sanal zemini özlüyorsanız, o zaman 1. ve 2. düğüm arasındaki sanal bir kısa hakkında konuşabilirsiniz.

Şek. 1. Op-amp ters çeviren entegratör (yalnızca negatif güç kaynağı V- açıkça gösterilir)

Harika fikri görmek için burada mevcut yol çok önemlidir. Giriş voltajı pozitif olduğundan, op-amp çıkış voltajı negatiftir ve akım op-amp çıkışına girer ... daha sonra negatif güç kaynağı V- 'den geçer ve giriş kaynağına geri döner. Bu durumda pozitif V + kaynağı gerekli değildir; yani sadece ima edilmiştir.

2. Elektrik eşdeğer devresi. Cevaplanması gereken ana soru şudur: "Op-amp burada ne yapıyor?" Girişleri arasında neredeyse sıfır voltaj tuttuğunu biliyorsunuz, böylece çıkış voltajı her zaman kapasitördeki voltaj düşüşüne eşittir. Dolayısıyla op-amp çıkışı, aşağıdaki voltaj kaynağı olarak işlev görür. O zaman bu elektronik devreyi basitleştirmek için op-amp'i değişken voltaj kaynağı VOA ile değiştirelim - Şekil 2. Bu arada, 2001 yılında laboratuvarda yüksek kapasiteli bir kapasitör kullandığımızda öğrencilerimle böyle gerçek bir deney yaptım ve 1 ile 2 arasında sıfır göstergesi bağlı.

Şek. 2. Elektrik eşdeğer devresi

Bu basit numara, devrenin arkasındaki harika fikri göstermek için yeterlidir. Voltaj kaynağı VOA, kapasitör C'ye seri olarak bağlanır, böylece voltajı, kapasitör boyunca voltaj düşüşünü VC telafi eder ve iki düğüm 1 ve 2 arasındaki voltaj (neredeyse) sıfırdır. Sonuç şu:

Ters çevirici amplifikatörün devresindeki op-amp , serisine eşdeğer voltaj VOA = VC ekleyerek kapasitördeki voltaj düşüşünü VC telafi eder.

Dolayısıyla, bu açıklamanın kilit noktası 'yu ekleyerek 'yi güçlendirmek değil. Negatif bir geri besleme devresindeki amplifikatörü bir amplifikatör olarak değil, entegratör gibi bir şey olarak düşünmek, bu tür op-amp devrelerini sezgisel olarak anlamak ve açıklamak için güçlü bir tekniktir. Aslında, burada biraz garip görünüyor (entegratör içinde entegratör) ... ama işe yarıyor ...

Bu "sihirli tarif" ne kadar basit ... Kusurlu RC entegratörünü mükemmel yapmak mı istiyorsunuz? Ardından kondansatöre seri olarak voltaj VC'ye sahip küçük bir değişken "pil" bağlayın ve (sonraki parlak fikir) ters "kopya" voltajını çıkış olarak alın. Yük, bu "yardımcı" kaynaktan gelen akımı tüketecektir ... giriş kaynağından değil (yani, bu arabelleğe alınmış bir çıktıdır ).

Bu sezgisel açıklamanın gücü, bu sofistike op-amp devresini "altı yaşındaki" bir çocuğa (Einstein) açıklayabilmemizdir ... ve bu, onu kendimiz anladığımız anlamına gelir ...

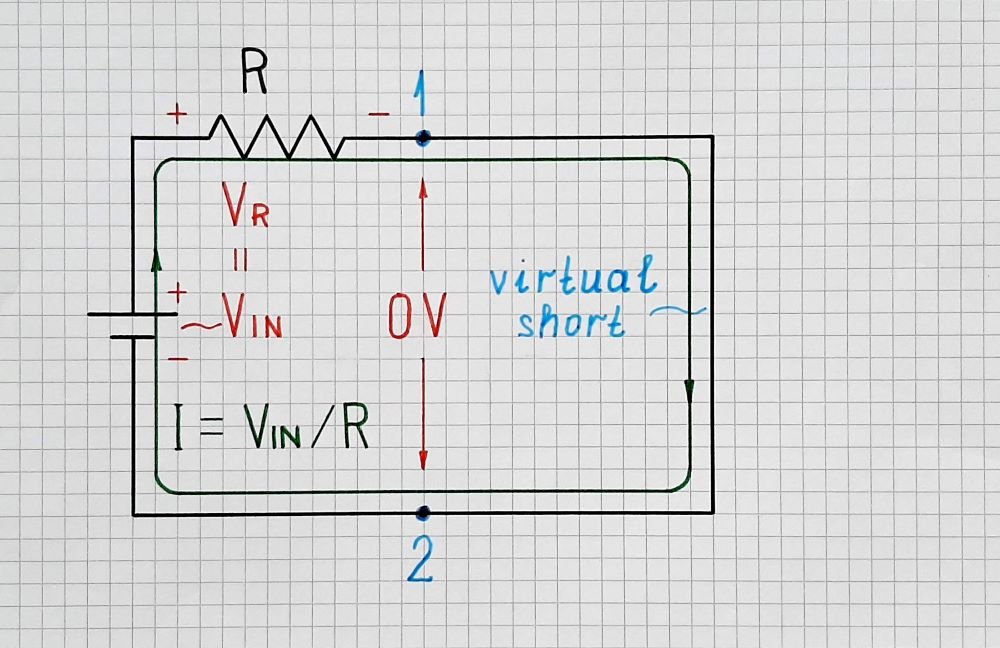

3. Sanal kısa Seri haldeki iki elemandan oluşan ağ üzerindeki toplam gerilim - bir kapasitör C ve dengeleyici gerilim kaynağı (VOUT), her zaman sıfırdır. Dolayısıyla bu ağ, 1. ve 2. noktaları kısaltan bir "kablo parçası" gibi davranır - Şekil 3. Bu, giriş kaynağının op-amp girişindeki R direncine "bakarken" "gördüğü" şeydir.

Şek. 3. Sağdaki çıkış kısmının eşdeğer devresi

Mecazi olarak konuşursak, op-amp çıkışı "negatif kapasitör" görevi görür. "Pozitif kapasitör" C, voltajını VC giriş voltajı kaynağından çıkarırken, op-amp "negatif kapasitör" voltajını VOUT giriş voltajına ekler.